近日,台积电举办了2021年技术研讨会,分享其先进逻辑技术、特殊技术、3DFabric先进封装与芯片堆叠等方面的最新进展,由于疫情尚未平复,台积电依然沿用去年的线上模式举办这次论坛。

“数字化转型为半导体行业开辟了一个充满机遇的新世界,我们的全球技术研讨会强调了我们增强和扩展技术组合的许多方法,以释放客户的创新,”台积电CEO魏哲家在大会上说道。

台积电将其领先的工艺节点分为三个产品家族:7nm、5nm和即将推出的3nn工艺节点,正如许多人在过去几年中注意到的那样,台积电自2018年推出7nm节点并实现大规模量产后,在芯片制造领域超越竞争对手取得领先地位,到今天也还是如此。

迄今为止,台积电7nm芯片出货已超过10亿颗,已经被纳入越来越成熟的工艺。且随着许多客户迁移到更先进的工艺节点,7nm产能增速放缓,预计2021年产能仅增加14%,与曾经16nm工艺系列产能进展类似。与之对应的,目前代工厂主要专注于5nm和即将推出的3nm芯片产品。台积电5nm工艺节点自2020年开始量产,为数以亿计的SoC提供动力,一方面越来越多的公司设计更多5nm产品,另一方面台积电拥有全球大约50%的EUV半导体设备,因此台积电5nm进展十分顺利,更是在此次技术研讨会上又添新成员——N5A。

台积电官方介绍,N5A工艺旨在应对当今对计算能力需求不断增加的汽车应用,例如支持AI辅助驾驶和座舱数字化,N5A将当今超级计算机中所使用的技术引入汽车,在满足AEC-Q100 2 级以及其他汽车安全和质量标准的可靠性要求的同时,满足N5的性能、功率和逻辑密度。

由于有台积电汽车设计平台的支持,N5A计划于2022年第三季度上市。

3nm明年量产,5G射频将升级到6nm

台积电也透露了其4nm和3nm的最新进展。采用与N5几乎近相同设计法则的4nm加强版在性能、功耗和集体管密度上均进一步提升,通过逻辑的光学微缩、标准单元库的改进和设计规则的推动,N4的晶体管密度较N5提升6%。台积电还声称,N4自2020年技术研讨会上宣布以来进展顺利,预计2021年第三季度风险量产。

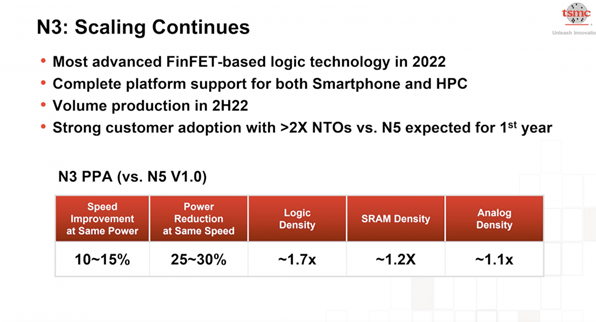

3nm方面,依靠业经验证的FinFET晶体管架构,得以实现最佳性能、功耗和成本效益,与N5相比,台积电N3性能提升15%、功耗降低30%、逻辑密度增加70%,有望在2022年下半年开始量产,同时成为世界上最先进的芯片制造技术。

拥有庞大市场的手机SoC制程的更新换代已不足为奇,如今5nm已经成为旗舰手机的标配,随着台积电3nm开始量产,可以预测各家手机厂商的旗舰手机SoC也将更新至3nm。不过射频芯片没有像手机SoC制程一样频繁升级,依然使用16nm左右制程,但这一局面可能会在未来有所改变。

与4G相比,5G智能手机需要更大的芯片面积、消耗更多的电量才能提供更高的无线传输速率,支持5G的芯片集成很多功能和组件,尺寸变大且与电池竞争空间。因此,本次研讨会上,台积电首次推出N6RF工艺,将其先进的逻辑工艺的功耗、性能和面积优势带到5G射频(RF)和WiFi 6、WiFi 6E解决方案中,预计N6RF晶体管性能将比上一代16nm射频技术高出16%以上。

此外,台积电还称,N6RF支持低于6GHz和毫米波频段的5G射频收发器,降低功耗和面积,且不会影响为消费者提供的性能、功能和电池寿命台积电N6RF还将增强WiFi 6/6E的性能和电源效率。

台积电还公布了其在先进封装方面的最新进展。

在高性能计算应用领域,台积电将在2021年为其InFO_oS 和 CoWoS封装解决方案提供更大的光罩尺寸,从而为小芯片和高带宽内存集成提供更大的二维平面。此外,台积电的SoIC-CoW预计今年完成N7对N7的验证,并将于2022年在全新的全自动化晶圆厂中开始生产。

在移动应用领域,台积电推出InFO_B解决方案,制造将强大的移动处理器集成在薄而紧凑的封装中,性能增强、电源效率变高,并支持移动设备制造商在凤装饰的DEAM堆叠。

值得注意的是,在同期举行的Computex大会上,AMD展示了其3D小芯片的首个应用,并称通过与台积电的密切合作,其3D小芯片技术比当前的3D封装解决方案耗能更少,堆叠更灵活。AMD同时表示,有望在2021年底之前开始生产具有3D小芯片的高端计算产品。